# LOW-POWER RETENTIVE TRUE SINGLE-PHASE-CLOCKED FLIP-FLOP WITH REDUNDANT-PRECHARGE-FREE OPERATION

## Mrs.M.NAVYA PADMA PRIYA<sup>1</sup>, Ms. NURUKURTHI SUMA<sup>2</sup>

<sup>1</sup>Assistant Professor, International School of Technology and Sciences for Women, Rajanagaram, Andhra Pradesh-533294.

<sup>2</sup>Assistant Professor, International School of Technology and Sciences for Women, Rajanagaram, Andhra Pradesh-533294.

### **ABSTRACT:**

This study discusses a low power, broadband flipflop that uses a lot fewer transistors. One transistor is all that is clocked in the flip-flop style, often referred to as True Single Phase *Clocking (TSPC) flip-flop, by a brief pulse train.* The dominant colourful flip-flop is the truth single-phase clock (TSPC), which performs the flip-flop operation quickly and with minimal power. This paper presents a thorough comparison of the positive side set off True Single Stage Clocking Flip-flop designs currently in use. The flip-flop arrangement for True Single Phase Clocking (TSPC) is compact and uses less energy. Moreover, it can be employed in a variety of applications, including microprocessors, barriers, and digital VLSI clocking systems. At several shops, numerous flip-flops have been evaluated for power consumption and propagation latency. Using DSCH and MICROWIND tools, the power consumption, propagation delay, and power holdup item of the developed flip-flops are compared.

Keywords: TSPC, DSCH, Flip flop.

#### **I INTRODUCTION**

As the procedure has actually advanced, digital systems' performance has considerably boosted, and power intake has turned into a severe constraint. Additionally, IOT gadgets are commonly used in the Web of Points due to the Net's eruptive development (IOT). There are a number of uses for the Web of Points (IOT). Just a couple of instances include transportation, healthcare, and also intelligent settings. Such battery-powered or self-powered tools utilize lowpower parts. Flip-flops (FFs) are essential components that make up a significant quantity of the complete power. FFs frequently eat 50% or even more of the power consumed for procedures in the arbitrary reasoning field. Because of its redundant change of interior nodes when the input and output are in the very same state, flip-flops (FF) normally consume more than half of the random-logic power in a SoC gadget. For this reason reducing the power consumption of FFs can drastically reduce the quantity of power eaten by Digital systems. The transmission-gate flip-flop (TGFF) is the FF that is used one of the most often

in modern electronic systems. The TGFF schematic is shown in Figure 1. The TGFF is a close to threshold operation-capable, contentionfree FF. The most significant issue with TGFF is the substantial clock network. The internal nodes CKN as well as CKI toggle, and also the nodes CKN and also CKI drive a majority of transistors, despite the input data. Therefore, TGFF continues to consume a lot of power even when information website traffic is very little. To decrease FF's power use, corresponding clock signals must be made use of extra precisely.

Flip-flops are the fundamental building blocks of the information path framework. They allow for information, the storage of refined by combinational circuit and synchronization of procedure at a provided clock frequency. They are the essential foundation of the digital electronic devices systems utilized in computers and many other sorts of systems. Flip flop can be either straightforward or clocked; easy gadgets are called locks. A latch is level delicate, as well as generally utilized as storage component. And also clocked gadgets are referred to as flip-flop. Flip-flop is side sensitive means their result just alters on a solitary kind of clock edge (favorable or unfavorable going side). Flip-Flop is a digital circuit that stores the rational state of one or more information input signal in response to a clocking pulse. They are often made use of in computational circuits to run in chosen sequences

throughout reoccuring clock intervals to get and also maintain information for a minimal amount of time enough for various other circuits within a system to additional procedure information [1] Information is saved in flip-flop at each rising and falling edge of clock signal to make sure that it can be applied as inputs to various other combinational or sequential circuits, such flip-flops that keep data on increasing or dropping edge of clock are referred as solitary side activated flip flops as well as the flip-flops that keep information on both the rising and falling edge of a clock pulse are referred as dual edge triggered flip-flops. In the earlier period, the VLSI developers were extra bent in the direction of the performance and also location of the circuits. Price and also Integrity additionally obtained core importance whereas power intake was a peripheral consideration for them.

Over the last few years, however, this has begun to alter quickly as well as power is being offered equal value in comparison to location and also rate [2] The major concerns in the performance arepower dissipation and propagation delay. Power usage is one of the standard restrictions in any incorporated circuit. There is always a trade- off between power as well as efficiency [3] In CMOS circuit there are 3 sources of power dissipation, first static (leakage) power dissipation which is related to the sensible states of the circuits as well as independent of switching task. Secondly is short circuit power dissipation when both NMOS and PMOS transistor in the circuit is turned on all at once for brief period of time throughout changing. And also because of this direct current path between powers supply and ground is formed. As well as 3rd is Dynamic (switching) power dissipation which is brought on by power dissipation during changing activity [4] Another vital timing worth for a flip-flop is the clock-tooutput hold-up i.e. the time taken by a flipflop to alter its outcome after the clock side. In electronic devices. the power-delay item which is additionally known as switching energy, is FOM (figure of advantage) correlated with the energy efficiency of a reasoning gateway. Power delay item is used to assess the performance of CMOS process. When the modern technology scales down, overall power dissipation decreases and at the same time delay varies depends upon supply voltage, threshold voltage, aspect proportion, oxide density, and load capacitance [5] This paper is organized as complies with. Section II talks about a brief literary works review as well as presents the style as well as work with real solitary stage clocking flip-flop. Section III provides format simulation of different layout of TSPC flipflop. Section IV offers outcome analysis of side set off TSPC flip-flop. Area V ends the paper as well as offers the future instructions.

#### **II RELATED STUDY**

Many designs for flip-flops have been suggested in literature. Recently, numerous methods in addition to various flip-flops have been suggested to reduce clock system redundancy. Several flip-flops are being distributed with the literature. [8] - [10] Master-slave and pulsetriggered flip-flops are accurately used in many digital and computational devices. [6] Shown in [5] and [7] are tiny area bright TSPCL (True Single Phase Clocked Logic) D flip-flops. These side set off flipflops have a low transistor count, which results in their small size. To conserve energy, some of these flip-flops' internal changes can be reduced with a simple modification. [7] The TSPCL dynamic logic design minimises complexity by using just one clock signal for synchronisation. D flip-flops are utilised in the TSPC flip-flop design and have a side set off (positive or negative). The circuit features nblocks and pblocks, which have alternating phases, and each block is driven by the same clock signal. Fig. 1 contains the schematic for the first TSPC flipflop. To simplify the design, just one global clock signal needs to be generated and distributed when using this layout. The traditional D flip-flop is shown in Fig. 1's dsch schematic, and the TSPC D flip-flop with 10 transistors is shown in Fig. 2's schematic. This edge-set off flipflop uses just one clock signal for synchronization. It is configured so that the input is isolated from the outcome when the clock signal clk is LOW.

The output will definitely latch the enhancement of the input when the clock performs a LOW-to-HIGH transition.

#### **EXISTING DESIGN:**

Several researchers are interested in creating low energy VLSI layout approaches that are almost adequate, as opposed to a typical approach, which has been predicted to become more well-known in recent months [3]. Modern device era essential physical barriers occur frequently, therefore new generations are being generated for processing. As a result, this advancement in integrated circuits has undoubtedly increased the demand for a VLSI chip with low power. The Intel 4004 CPU, released in 1971, had 2300 transistors and consumed electricity at a rate of 1 watt per cycle. The Pentium grew more advanced after that, in 2001. When operating at 2.4 GHz, it dissipated 65 watts of energy while protecting 42 million transistors. In a few years, a comparable computer will have the same electricity as an atomic power plant if energy densities rise quickly. Because to problems with thermal stress, electromigration, and heated spots, such high-energy thicknesses increase concerns about tool damage and performance loss. Another reason that has raised market demand for all mobile consumer electronics devices that need batteries is lower electricity chips, which in turn use gas. The need for more compact, lighter, and longer-lasting

digital products is essential for consuming less energy. Electronic devices also produce more heat due to increased electricity consumption, necessitating more expensive cooling solutions, such as fluid air conditioning racks for computers, which increases the overall cost of the ICequipped equipment.

#### **III RECOMMENDED SYSTEM**

In VLSI design, POWER reduction has truly become a top priority. In typical CMOS devices, vibrant and leak power are suppressed using a number of common techniques. Pipelining and subsequent voltage scaling are two of the most effective methods for reducing power dissipation at a given operating frequency. However, at high operating frequencies, the power and delay costs of pipe signing up become significant and also impair overall system efficacy. Cost recovery circuits have the ability to use less power than their pipelined, voltage-scaled CMOS counterparts in systems with significant changing job. There have been many charge-recovery logic styles proposed [1]- [5]. When compared to voltagescaled CMOS, these charge-recovery techniques have been shown to produce lower energy dissipation throughout a range of relatively low operating regularities (a few hundred megahertz). Energy cost savings over CMOS at higher operating frequencies, however, have remained elusive. Common operating regularities in chargerecovery circuits are more a result of design than any kind of basic constraint, even though performance limitations of charge-recovery circuits are fundamentally determined by the need for slowly transitioning power-clocks. Utilizing diode-connected transistors [6–7], employing pMOS tools in evaluation trees [8–9], and taking an excessive amount of time to solve the complementary outputs of dual-rail gates during evaluation [2–4–10] are some of the main factors that lower rates in charge-recovery circuits.

The concept of Boost Logic is illustrated in Fig. 1(a). Each Increase Logic gate has two parts that operate simultaneously over discrete time intervals: a charge-recovery phase and a conventionally switching logical assessment phase (Reasoning) (Boost). Simplified voltage waveforms of a Boost Logic gate result are shown in Fig. 1(b). Logic resolves the output nodes to supply rails as well in the initial stage of operation. The second part of Boost's functioning involves forcing the results to follow the appropriate echoing clock signals and oscillate at peak voltage, which amplifies the voltage differential between the outcomes. These clocks will undoubtedly be referred to as power-clocks moving forward. A gateway overdrive is provided to fanout Logic stages by this full-rail swing, allowing them to perform evaluation at regularities much higher than those predicted of such boldly voltage-scaled reasoning. Although hostile voltage

scaling in Reasoning is made possible by Boost, significantly reducing power dissipation, it is crucial that the power dissipation of Boost itself does not negate these advantages. As a result, Reasoning provides an initial voltage difference to boost, greatly assisting its sense-amplifying function and also causing successful chargerecovery. Although previously proposed reasoning homes have utilized bootstrapping procedures to make use of the concept of enhanced gateway overdrive [3], [12], these strategies lack the sturdiness offered by the utilization of an Increase phase. The amount of gate overdrive that may be used with these techniques is also constrained. More recently, LVS reasoning has been advocated [13], where sensation amplifiers are used to improve the results of low-swing entrances.

Through in-depth simulations, we were able to determine the performance and energy-efficiency of Increase Logic. In particular, we have established how resilient Boost Reasoning gateways are to clock skew. Additionally, we looked into how different power sources affected the efficiency and effectiveness of Boost Reasoning. We have actually constructed 1-bit FF-D and also T in both Increase Logic and also pipelined, voltage-scaled static CMOS to fairly review the power effectiveness of Increase Reasoning. Both FF were designed to function at 1 GHz. Increase Reasoning outperforms its minimum-energy fixed counterpart in terms of power efficacy by about 5 times, but at the cost of 3 times more latency.

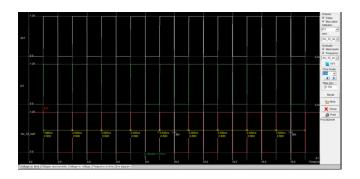

#### CIRCUIT1:

Figure a) Representing the Simulation of Layout diagram of proposed circuit 1

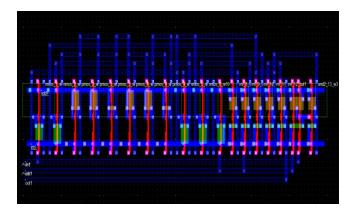

Figure b: Representing the Layout model for circuit one

### **CIRCUIT 2:**

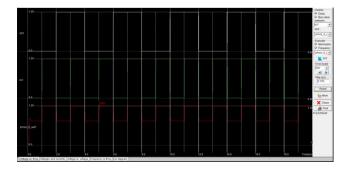

Figure a) Representing the Simulation model on 90nm

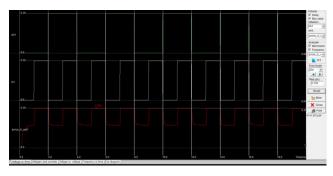

Figure a) Representing the Simulation model on 32nm

#### CONCLUSION

It has been envisioned how lots strength the clock and the relaxation of the turn-flop use up throughout a spread of switching operations. It is plain that using the sleep alternative on SCCER and DCCER turn-flops will bring about decrease strength intake than the use of the prevailing design for the clock and the the rest of the circuit. The format model that is suggested functions a Dual D- FF with and without Uncommitted difficulty. When as compared to the SCCER flip-flop layout for the sleep putting, this design has proven drastically better results. This architecture performs as a T-FF instead of a D-FF in an lively environment, giving it advanced overall performance versus a DCCER flip-flop. There isn't any clock overload while the clock gating scheme is implemented. Due to their favourable strength and latency traits, SCCER turnflops may be used in adiabatic clocking in digital structures.

#### REFERENCES

[1] M. A. Hernandez and M. L. Aranda, "A Clock Gated Pulse-Triggered D Flip-Flop for Low Power High Performance VLSI Synchronous Systems," Proceedings of the 6th International Caribbean Conference on Devices, Circuits and Systems, Mexico, pp. 293-29, 28 April 2006.

[2] M. Pedram, "Power minimization in IC Design: Principles and applications," ACM Transactions on Design Automation of Electronic Systems, Vol. 1, pp. 3-56, Jan 1996.

[3] B. Nikolic, "Design in The Power Limited Scaling Regime," IEEE Transaction on Electronic Devices, Vol. 55, No. 1, pp. 71-83, January 2008.

[4] Neil H. E. Weste, David Harris, Ayan Banerjee, "CMOS VLSI DESIGN: A Circuits and Systems Perspective", Third Edition, 2007.

[5] Surya Naik and Rajeevan Chandel, "Design of a Low Power Flip-Flop Using CMOS Deep Submicron Technology", IEEE International Conference on Recent Trends in Information, Telecommunication and Computing (ITC), pp. 253-256, 2010.

[6]Z. Peiyi, M. Jason, K. Weidong, W. Nan, andW. Zhongfeng, "Design of Sequential Elements for Low Power Clocking System". IEEE Transaction on Very large Scale Integration, pp. 914-918, July 2010.

[7] Mohamad Elgamel, Tarek Darwish and Magdy Bayoumi, "Noise Tolerant Low Power Dynamic TSPCL D Flip- Flops", IEEE Annual Symposium on Very Large Scale Integration (ISVLSI.02), pp. 80-85, 2002.

[8] P. Zhao, T. K. Darwish, and M. A. Bayoumi, "High-Performance and Low-Power Conditional Discharge Flip-Flop", IEEE transactions on very large scale integration (VLSI) systems, Vol.12, No.5, pp. 477-484, May 2004.

[9] C. K. Teh, M. Hamada, T. Fujita,H. Hara, N. Ikumi, and Y. Oowaki, "Conditional Data Mapping Flip-Flops for Low-Power and High-Performance Systems", IEEE Transactions on very large scale integration (VLSI) systems, Vol. 14, No. 12, pp. 1379-1383, December 2006.

[10]Bhuvana S, Sangeetha R, "A Survey on

Sequential Elements for Low Power Clocking

System", Journal of Computer Applications,

ISSN: 0974 – 1925, Vol. 5, 10 February 2012.